——内容参考《Tessent™ MemoryBIST User’s Manual For Use With Tessent Shell》 Appendix A

TCD(Tessent Core Description)文件可用于描述Memory的端口及行为,用于Tessent Memory BIST流程,Memory的TCD文件可以由LogicVision memory library格式的文件转为TCD,LogicVision文件由Memory Compiler工具产生,后缀为logicv.lib。

简介

在tshell(Tessent Shell)中,TCD可用于描述memory library、boundary scan information或fuse box interface,读入之后以Core Wrapper的形式在tshell内部存储,每个module name是唯一的,这里module_name就是design top name:

Core(module_name) {

Memory {

}

MemoryCluster {

}

BoundaryScan {

}

FuseBoxInterface {

}

}TCD可以通过read_core_descriptions命令读入(tshell可以读入Memory的logicv.lib文件,自动转为TCD格式,):

read_core_descriptions *logicv.lib通过report_config_data读出:

report_config_data -partition tcdMemory

一个完整的Memory TCD文件格式如下:

Core(module_name) {

Memory {

Algorithm : algo_name;

ATD : on | off;

BitGrouping : int | auto;

ConcurrentRead : on | off;

ConcurrentWrite : on | off;

DataOutHoldWithInactiveReadEnable : on | off;

DataOutStage : none | StrobingFlop

InternalScanLogic : on | off;

LogicalPorts : nRnWnRW;

MemoryHoldWithInactiveSelect : on | off;

MemoryType : rom | sram | dram;

MilliWattsPerMegaHertz : real | auto;

MinHold : time; // default: 0

NumberOfBits : int | auto;

NumberOfWords : int | auto;

ObservationLogic : on | off;

OperationSet : operation_set_name;

PipelineDepth : int; // default: 0

ReadOutOfRangeOK : on | off;

RetentionTimeMax : time | none;

RomContentsFile : file_path_name;

ShadowRead : on | off | auto;

ShadowWrite : on | off;

ShadowWriteOK : on | off;

TransparentMode : syncmux | none | asyncmux;

Port(port_name) {

}

AddressCounter {

}

PhysicalAddressMap {

}

PhysicalDataMap {

}

GroupWriteEnableMap {

}

RedundancyAnalysis {

}

IclPorts {

}

}

}Algorithm: algo_name

指定MBIST算法,最常用的是SMarchCHKBvcd算法。

ATD(address transition detection): on | off

开启或关闭地址跳变检测,相当于Memory的AT-Speed测试,检测地址的跳变是否满足spec的时序要求。

BitGrouping : int | auto

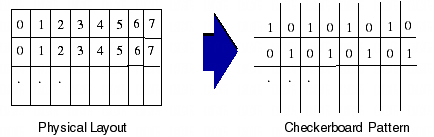

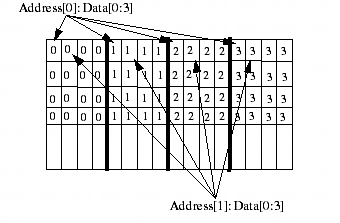

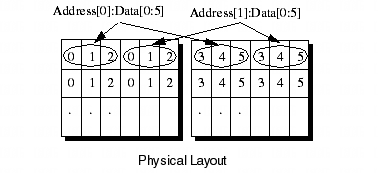

描述Memory中一个word的物理分布情况,一个word的bit位可以在同一行紧挨在一起,也可以间隔分布,不同的分布会影响测试算法的生成,以下是几个示例:

1、这是一个8bit的memory,MBIST controller需要在物理相邻的位置上交替写入0、1,这种情况下,BitGrouping=8:

2、 一个4bit位宽的memory示例,每个word的4个bit间隔分布,BitGrouping=1:

3、一个6bit位宽的memory示例,一个word中的前3bit为一组,后3bit为一组,间隔分布,BitGrouping=3:

ConcurrentRead: on | off

针对多端口的memory,开启后可以在测试算法对active port读写时同时对inactive port读,用于测试多端口之间的耦合故障,需要用户提供对应的operation sets,默认为off。

该选项开启后,会在memory interface上插入额外的电路。

ConcurrentRead相较于ShadowRead更加灵活,可以指定row(word)和column(bit) address,ShadowRead仅能指定row address。

ConcurrentWrite: on | off

与ConcurrentRead类似,相较于ShadowWrite灵活性更高,可以由自定义的operation sets控制,ShadowWrite 只支持library algorithms,不支持自定义operation set。

默认值为off。

使用这个选项,需要memory至少满足如下条件中的一个:

- Two ReadWrite ports(真双端口)

- One Read-only port and one Write-only port

- Any number of Read-only ports and two Write-only ports

DataOutHoldWithInactiveReadEnable : on | off

指定当memory的read enable无效时,输出是否保持原值,这个选项会影响SMarchCHKBvcd算法行为,默认值是off,根据memory实际特性设置。

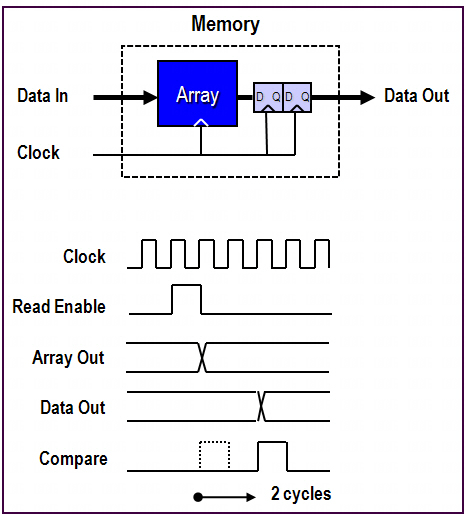

DataOutStage : none | StrobingFlop

可以选择是否在memory data output加一级选通寄存器,用于满足memory的读后写的hold time?加入这个选通寄存器实际上在data output 和 comparator 逻辑之间加了一级pipe,默认值为none。

这个选通寄存器还会在scan时被用于bypass,受参数 TransparentMode 控制。

InternalScanLogic : on | off

这个参数用于指定memory是否有内部的scan逻辑,通常是指bypass logic中的DFF(在datain和dataout之间),通常memory的bypass逻辑是tshell在外部插入的,这个选项默认为off,如果memory内部有bypass,则需要开启这个选项,并且提供memory scan model,并且将Core/Memory/ObservationLogic设为off,这个选项用于tshell生成address和control inputs的observe logic,同时需要设置 TransparentMode 为none。

LogicalPorts : nRnWnRW

指定memory的read write port。

nR:read port number

nW:write port number

nRW:ReadWrite port number

sram的默认值是1RW,rom的默认值是1R,rom不能指定W或RW,sram至少要指定(1R、1W)或1RW。

MemoryHoldWithInactiveSelect : on | off

用于指示,当片选信号无效时,memory内容是否保持,并且memory的输出是否保持上一次read的输出,默认情况下为on。

这个选项会影响SMarchCHKBvcd算法的行为。

MemoryType : rom | sram | dram

默认为sram。

MilliWattsPerMegaHertz : real | auto

描述power与frequency之间的关系。

默认为auto,计算公式为b (0.0004 + (c 0.00008)),其中b是bits per word,c是column或counm mux的数量,

MinHold : time; // default: 0

这个参数提供RTL阶段仿真时,BIST controller输出address、data和控制信号相对clk的delay,这个delay不会影响综合,综合时的holdtime约束还是依靠sdc保证。

单位为ns,最多两位小数,默认是0,这个值不能大于clk period,否则报错。

NumberOfBits : int | auto

bits per word,如果没指定,默认值是第一个logical port的output data width,一个32X8的memory,表示depth=32,bits per word=8。

NumberOfWords : int | auto

number of words,这个值默认为AddressCounter字段中定义的columns*rows*banks。

如果指定了AddressCounter/CountRange,则使用这个值,如果没指定,则默认是$2^n, n=address width$ 。

对于non-segmented addresses或者实际地址范围不是2的幂的memory,需要指定NumberOfWords,否则可能会导致仿真失败。例如一个地址位宽为4bit的memory,实际只有12个words,如果不指定 NumberOfWords 就会仿真失败。

MBIST controller支持非对称bank(每个bank有不同数量的rows)的memory测试。这种情况下,必须为每个memory address segment指定AddressCounter/CountRange。并且需要指定NumberOfWords,表示真实的memory地址范围为0到NumberOfWords-1。

对于32X8的memory,NumberOfWords为32。

问题:什么是non-segmented addresses?

ObservationLogic : on | off

用于指示tshell是否在memory interface中为address和control signal加入scan observation point。

设置为on会加入XOR gate和寄存器,提供observation,tshell会使用interface中已有的寄存器,如果有必要,也会添加额外的寄存器。

OperationSet : Async | AsyncWR | ROM | (Sync) | SyncWR | SyncWRvcd |TessentSyncRamOps | TessentSyncRamOpsHR4 | TessentSyncRamOpsHR6 |OperationSetName

指定operation set的名字,MBIST controller会根据operation set生成波形。operation set定义的operation必须能algorithm的需求。

Async | AsyncWR | ROM | (Sync) | SyncWR | SyncWRvcd | TessentSyncRamOps |TessentSyncRamOpsHR4 | TessentSyncRamOpsHR6

以上这些是tshell的保留的library operation set,用户也可以自定义。

Tip: 推荐使用libraty operation set作为模板,定义custom operation set,因为library中的是比较通用的,没有针对某种特定memory做优化。Custom operation sets可以满足特定的时序需求。

OperationSetName是用户定义的标识,tshell会搜索与之匹配的库文件(由用户提供)。

Library Operation Sets:

Async: 用于没有clock的RAM,包括三个operation,Write、Read和ReadModifyWrite。每个operation需要4 cycles(这里的clock是指MBIST controller的reference clock)。在Read和ReadModifyWrite中加入了基础的shadow read操作。这个operation set很少用于现代memory了。ReadModifyWrite:读-改-写,对于不支持按位写的memory,如果需要改动一个word中的部分位,就需要先读出,修改部分位,再写入。AsyncWR:是Async的一个变体,每个operation由4个cycle变为了6个,并且在Write操作时也加入了shadow reads。ROM:用于ROM,通常与ReadOnly library algorithm组合使用,它只包含两种operation,Read和CompareMISR,每个operation执行2 cycle,对于有无clock的ROM均可使用。Sync:用于同步RAM(有function clock),有三个operation,Write、Read和ReadModifyWrite,每个operation执行2 cycle,在Read和ReadModifyWrite中加入了基础的shadow read操作,它与大部分library algorithms都兼容。SyncWR:Sync的一种变体,区别是在Write时也加入了shadow read。SyncWRvcd:SyncWR的一种扩展,通常与SMarchCHKBvcd库算法结合使用。包含12个operation,每个operation执行2-3个cycle。

operation list如下,它提供了更为完整的memory测试,例如bit/byte write enable、read enable以及select信号的测试。还加入了并行读写,提高了多端口memory测试的覆盖率。

| Code | Operation Name |

|---|---|

| OP0 | NoOperation |

| OP1 | Write |

| OP2 | Read |

| OP3 | ReadModifyWrite |

| OP4 | ReadModifyWrite_WithSelectOff |

| OP5 | WriteReadCompare |

| OP6 | WriteReadCompare_EvenGWE_On |

| OP7 | WriteReadCompare_OddGWE_On |

| OP8 | WriteReadCompare_AllGWE_Off |

| OP9 | ReadWithReadEnableOff |

| OP10 | ReadModifyWrite_Column_ConcurrentWriteRead |

| OP11 | ReadModifyWrite_Row_ConcurrentWriteRead |

| OP12 | WriteRead_Column_ConcurrentReadWrite |

TessentSyncRamOps:SyncWRvcd的一种扩展,包括25个operation,每个执行2-3 cycle,它支持所有library算法的实现,以及一些lib/technology/memory_bist/algo文件加中的文献中的一些算法。TessentSyncRamOpsHR4:TessentSyncRamOps的一种变体,区别是在Read operation中,包括4个连续读,TessentSyncRamOps只包含两个连续读,旨在第一次读时compare。TessentSyncRamOpsHR6:TessentSyncRamOps的一种变体,区别是Read operation中包含6个连续读,同样也是只在第一次读时compare。

Custom Operation Sets:

标准的library operation sets只支持有同步读写port的memory(对应Sync*OperationSets),或异步读写port(对应Async*OperationSets)。如果一个memory同时有同步写和异步读端口,就需要custom operation set了。

对于异步读的memory,当read enable有效时,read data输出立即有效(同拍),在operation set中,StrobeDataOut(表示需要compare read data)需要在第一个Tick中写,以下的custom operation set可用于有同步写和异步读端口的memory:

OperationSet (SyncW_AsyncR) {

Operation (Write) {

Tick {

WriteEnable : On;

ShadowReadEnable : On;

ShadowReadAddress : On;

}

Tick {

WriteEnable : Off;

ReadEnable : On;

ShadowReadAddress : Off;

}

}

Operation (Read) {

Tick {

StrobeDataOut;

ReadEnable : On;

ShadowReadEnable : On;

}

Tick {

ReadEnable : On;

ShadowReadEnable : On;

}

}

Operation (ReadModifyWrite) {

Tick {

StrobeDataOut;

ReadEnable : On;

ShadowReadEnable : On;

}

Tick {

WriteEnable : On;

ReadEnable : Off;

ShadowReadAddress : On;

}

}

}PipelineDepth : int; // default: 0

定义compare操作的pipeline,当memory内置pipeline时(read data需要多拍传出),需要指定这个参数。

这个参数可以将同一种operation set用于不同pipeline的memory。

当你的operation set如下:

Operation (Read) {

Cycle {

read_enable: on;

}

Cycle {

read_enable: off;

strobe_data_out: on;

}

}第一个cycle表示读取数据,第二个cycle中strobe_data_out表示compare,如果一个memory内置了两拍延时,则可以指定PipelineDepth=2,不需要改动operation set,controller会产生对应的延时两拍波形。

ReadOutOfRangeOK : on | off

告知EDA工具memory是否能够容忍超出地址范围的读操作。当开启了ShadowRead时,读操作是可能超出地址范围的,Controller中默认需要检查地址范围是否超出。如果将ReadOutOfRangeOK 设为on,则不检查。超出地址范围的read是不会影响BIST的结果的。但是,如果memory会因为这个操作而损坏数据,则必须设为off。

RetentionTimeMax : time | none

RetentionTimeMax属性指定DRAM阵列两次完全刷新之间的保留时间上限。因此,应用于DRAM的两个连续刷新操作之间的实际刷新间隔计算为RetentionTimeMax除以最大DRAM行数,默认值是none。

RomContentsFile : file_path_name

指定ROM中的二进制内容,file中每行都是一个word的数据,首地址为0,支持2进制和16进制两种格式,在同一个file中,两种格式不能混用。

可以使用DftSpecification/MemoryBist/Controller/Step/MemoryInterface wrapper中的rom_content_file覆盖ROM content file name。

ShadowRead : on | off | auto

用于开启或关闭shadow read cycle。shadow read用于检测多个logical port之间的短路,MBIST controller会在读写active port的同拍,对inactive port读。shadow read不支持对不同列进行读(按位读),使用ConcurrentRead更灵活。

设为on时,shadow read将会对row address counter(word address)的bit0取反,在inactive port读该地址。设为off则关闭shadow read。

如果设为auto,EDA工具在以下情况下会自动关闭shadowread:

- 当OperationSet字段没有指定

ConcurrentPortSignals/read_row_address和ConcurrentPortSignals/read_enablewaveforms时 - 如果没有在

AddressCounterwrapper中指定row address - 如果使用默认的address counter并且NumberOfWords的值是奇数

- 如果lowRange for

Function(RowAddress)/CountRange是奇数,或者highRange forFunction(RowAddress)/CountRange是偶数(会导致read out of range)并且ReadOutOfRangeOK设为了off。 - 如果指定

LogicalPorts: 1RW or 1R

如果ShadowWrite设为了on,如果条件满足,ShadowRead会自动设为on。

当ConcurrentPortSignals/read_enablewaveform为on时,address counter禁止由于行地址取反造成的out of range。

ShadowWrite : on | off

用于开启或关闭ShadowWrite。shadow write用于检测port之间各个bitline的耦合故障。MBIST controller会在SMarchCHKBci、SMarchCHKBcil、SMarchCHKBvcd中特定的阶段在inactive ReadWrite ports上进行写操作。

对于有一个Read port和两个Write port的memory,SMarchCHKBci、SMarchCHKBcil、SMarchCHKBvcd算法支持在READ和WRITE阶段对inactive write port上写操作。

设为on时,shadow write会将row address设为最大值(原文:forcing the row address to its full binary range),进行写操作。

ShadowWriteOK : on | off

指定memory在shadow write时是否可以忍受地址out of range。当支持shadow write时,ShadowWriteOK 必须设为on。ShadoWrite operation只支持library algorithms,如果需要custom operation sets,可以使用ConcurrentWrite。

意味着shadow write是一定会out of range的?

TransparentMode : syncmux | none | asyncmux

定义memory在scan测试中,何时、如何bypass。

默认值是syncmux。

- syncmux:在memory output port上插入额外的mux和寄存器

- none:不在interface中加入bypass逻辑,当memory内部自带bypass逻辑时,需要设为none

- asyncmux:在output port上加mux,不额外加寄存器,输入可以直连到输出,这个值只有在

DataOutStage设为none时才可以被使用

Note:如果memory内部含有bypass电路,在进行MBIST flow时,必须禁用掉bypass逻辑